In this article I will elucidate a simple universal H-bridge module using BJTs and N-channel MOSFETs.

This module can be integrated with any standard oscillator ICs such as IC 4047 or IC SG3525 or even IC 555, to create a highly efficient H-bridge inverter circuits.

Why using 4 N-channel MOSFET H-Bridge is the Most Efficient

Using 4 N--channel MOSFETs in an H-bridge configuration is considered to be the most efficient topology because N-channel MOSFETs have much lower RDSon compared to their P-channel counterparts.

Lower RDSon means lower drain to source resistance, which ensures lower heat dissipation and higher current transfer across the MOSFETs.

The Challenge behind 4 N-Channel MOSFET H-Bridge

However creating a H-bridge using N-channel MOSFETs can be difficult since it involves a relatively complex a bootstrapping network.

The bootstrapping network refers to a small circuit network around the gates of the high-side MOSFETs which enables the high-side MOSFETs to conduct freely by ensuring that its gate voltage is always around 12V higher than its instantaneous source voltage.

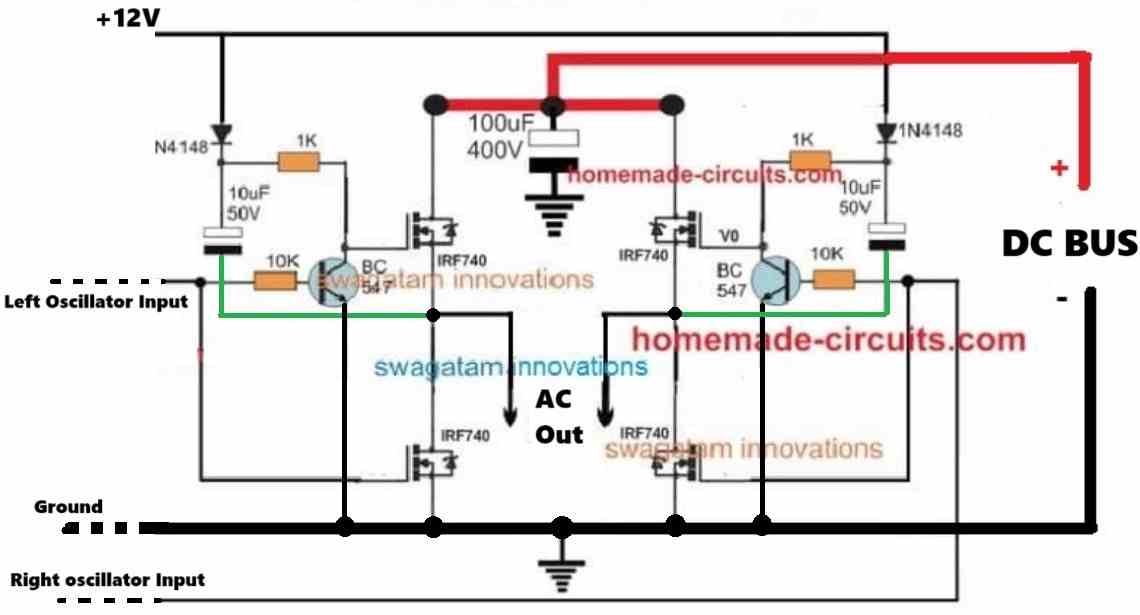

Now, let's try to understand how our universal H-bridge circuit module using N-channel MOSFETs works.

How the Circuit Works

If you don't want to read the following description, you can watch this video instead:

Referring to the diagram below, let's assume an instantaneous moment where the left side oscillator input is low, and the right side oscillator input is high.

In this situation, the left side BC547 is turned OFF due to the absence of the base switching voltage, and the left side 10uF/50V capacitor is charged up to the battery voltage level through the 1N4148 diode.

Now, the left high-side MOSFET gets its voltage through the 1N4148 diode, and the 1k resistor, and makes an attempt to conduct.

However, as soon as the MOSFET drain voltage reaches its source terminal and exceeds its gate voltage (12V), the conduction stalls, because as we know, ideally, for any MOSFET to conduct, its gate potential must be around 10V higher than its source potential.

This is where our BC547 and 10uF bootstrapping network comes into action.

When the Left high-side MOSFET drain voltage reaches the source terminal, this voltage is forced into the 10uF capacitor through its negative terminal.

This source voltage entering the negative terminal of the 10uF capacitor now comes in series with the existing 12V stored inside the 10uF capacitor.

So, as the source voltage rises it pushes the stored potential inside the 10uF higher so that the total voltage at the gate of the MOSFET is always 12V higher than the source voltage of the MOSFET.

So, when the source voltage is 12V, it adds up with the internal 12V of the 10uF capacitor producing 12 + 12V = 24V at the gate of the high side MOOSFET.

This means the effective gate voltage is now the difference between the total gate voltage and the source voltage, that is 24V minus 12V = 12V, or if suppose the drain supply is 100 volts, then the effective gate voltage will be 100 volts plus 12 volts minus 100 volts = 12 Volts

This ensures that the gate voltage of the high side MOSFET is always held at 12V higher than its source voltage.

This in turn enable the high side N channel MOSFETs to conduct freely and efficiently, regardless of the applied drain voltage level. This may not be possible if P-channel MOSFETs are used, although P-channel MOSFET wouldn't require a bootstrapping.

A High-side P-channel MOSFET might not require a bootstrapping, but the main disadvantage of using P-channel high-side MOSFETs is, its drain voltage cannot exceed the gate voltage, which simply means that if the oscillator IC output is 12V, then the load voltage cannot exceed 12V, which appears to be a big drawback, which is completely eliminated if N-channel MOSFETs are used.

That's it! this concludes our tutorial on a simple H-bridge circuit module using N-channel MOSFETs which can be used to transform any center tapped inverter into an H-bridge inverter.

I hope you liked the tutorial…. for any further doubts or queries, please feel free to comment below for quick replies.

Summary

The H-bridge inverter topology is the most efficient one, since it does not necessitate the use of center tap transformers, and allows the use of transformers with two wires. The results become even better when four N-channel mosfets are involved.

With a two wire transformer connected to an H-bridge means the associated winding is allowed to go through the push pull oscillations in a reverse forward manner. This provides better efficiency as the attainable current gain here becomes higher than the ordinary center tap type topologies.

However better things are never easy to get or implement. When identical type mosfets are involved in an H-bridge network, driving them efficiently becomes a big problem. It is primarily due to the following facts:

As we know an H-bridge topology incorporates four mosfets for the specified operations. With all four of them being N-channel types, driving the upper mosfets or the high side mosfets becomes an issue.

This is because during conduction the upper mosfets experience almost the same level of potential at their source terminal as the supply voltage, due to the presence of the load resistance at the source terminal.

That means the upper mosfets come across similar voltage levels at their gate and source while operating.

Since as per the specs, the source voltage must be close to the ground potential for efficient conduction, the situation instantly inhibits the particular mosfet from conducting, and the entire circuit stalls.

In order to switch the upper mosfets efficiently they must be applied with a gate voltage at least 6V higher than the available supply voltage.

Meaning if the supply voltage is 12V, we would require at least 18-20V at the gate of the high side mosfets.

Comments

thank you sir for your reply,

sir can I connect both 12v supply for bc547 and dc bus supply eachother

means can I use only one same dc positive supply to all circuit

thank in advance sir

Pravin, if the motor is also 12V, then you can use a single 12V supply for the whole circuit, but if your motor requires 24V then you will have to keep the 12V and the 24V sources separate. The ground can be a single common line for the whole circuit.

for 12 volt or 24 volt motor 400v 100uf capacitor required or not, this capacitor used in dc bus possitiv

Yes, it is required, you can can use a 100uF/50V capacitor, 400V is not required.

hello sir,

can I run 24 volt dc motor on this circuit,

like H bridge driver

Hello Pravin, yes, you can use it…

hello sir, I’m trying to build h-bridge inverter with egs002 module and 4 irfp460 mosfet, in which input supply voltage is around 400 volt dc.

How much continuous power can I get from that inverter and what will be the efeciency ?

plz help someone…

Thank you so much sir for your precious information.

You are most welcome!

Hello Mahesh,

The maximum power that you can achieve using the mentioned specifications is around 220 * 10 = 2200 watts, assuming the output voltage is 220V, and the maximum load current is 10 amps.

Sir,

I need information & circuit details of Interactive UPS PCB Board used in Zebtronics /Intex/Microtek used of PC. 600/850/1000 VA. This Board is common in all UPS with IRF3205 H Bridge MOSFET for 12 V or 24 V Dc Battery. Firing circuit is using oscillator UC3843A & Microprocessor of UPS.

Firing circuit involved W1P & W2F Smd Transistor in pair of 3 & 4 which i do not understand. I am facing Failure of MOSFET repeatedly.

Hi Ashish,

Sorry, unfortunately i do not have any information regarding the configuration used in Zebtronics /Intex/Microtek UPS.

However you can easily build a good H-bridge circuit using any standard H-bridge driver IC such as IR2110 or IRS2453(1)D and MOSFET IRF3205.

Hi Mr. Swagatam. Thank you for all your help in educating people like me in the world of electronics. You simply are Amazing!.

I need your help in this: I’m at about 85% into completing my 1.5KVA hbridge inverter with the help of one of your hbridge circuits. I use the MOSFETS in reverse for charging my battery. The challenge is that the charging system isn’t effective as low mains voltage would only be playing with the battery instead of charging it. So, I want to install a feedback in this hbridge circuit, how do I go about that?. Please help me.

Thank you Chinomso, I appreciate your kind words.

A feedback network can only enable reduction in voltage if there’s an excess input voltage, a feedback network cannot boost a low voltage situation, therefore adding a feedback to boost your low AC voltage may not be feasible.

Quick question about use of these inverters. I’m trying to modify a DC inverter welder to AC for TIG welding. Is there a way to use these circuits for such an application? I suspect there are factors that I’ve not considered or are aware of that will need to be addressed.

Thanks

Doug

You can definitely use a full bridge topology for quickly converting a DC source into an AC source. However, I won’t recommend the above circuits. You can instead try one of the following designs:

https://www.homemade-circuits.com/simplest-full-bridge-inverter-circuit/

Pls sir, why’s the ic4049 frequency fixed at 1khz instead of 500hz

I think there’s some confusion. The 3 pins of the 4017 IC which are joined with the mosfet gates must together generate 50 Hz frequency, that means each pin must generate 17 Hz frequency and the 4049 IC frequency should be 17 x 10 = 170 Hz. It is better to fix it by a practical testing

Hi, how would this circuit need to be modified to implement 2000vdc mosfets.?

Hi, I don’t recommend this circuit as it has some problems. You can refer to the following link:

https://www.homemade-circuits.com/?s=simple+H-bridge+full

sir thanks a lot for such innovation,but please can this circuit be suitable for 5ka,24v battery.And how can incorperate full and low battery cutoff with this circuit please.

Thanks Henry,

I won’t recommend this circuit since it is not a verified design. Please refer to the battery charger category to find the desired charger for your inverter.

thank you sir for your prompt reply

Plz sir,why was pin15 connected to pin 1 instead of pin 10 ?

To put a a single pulse gap between each pin, so that the output waveform is symmetrical.

Pls sir swag,how did u get the 4 pinouts that u multiplied with the 50Hz

Nimel the pin numbers are pin#3, 2, 4, and 7 of IC 4017

Hi, I do design inverter using sg3524n and its center tap base transformers.

Pls I need a circuit diagram of how to use H bride transformers.

Thanks

You can refer to the following article for the detailed instructions:

https://www.homemade-circuits.com/sg3525-full-bridge-inverter-circuit/

I want to try out the second design consisting of 555 and 4017 stage but I want to use irfp260N mosfet transistor will it be suitable to apply with the irf9540 p channel

Yes it is fine to use IRFP260N in the second design, but may not be the recommended one if the operational voltage across the MOSFETs is below 100V

sir if i can understand from this circuit>https://www.homemade-circuits.com/wp-content/uploads/2013/04/fullbridgeinvertercircuit.png ,is it right to note that the oscillator ic is the C4017?

Evans, the oscillator is 4049 IC, the 4017 is the alternate switcher for the H bridge

Hi sir

I am trying to develop a full bridge inverter using 555 timer and 4017IC, how can I do this. how much on time should I set for mosfets?

Hi Ganesh, you can try the last concept presented in the following article, by replacing the BJT stage with a 4017 stage.

https://www.homemade-circuits.com/simplest-full-bridge-inverter-circuit/

Hi sir,am Evans do you mind sending circuit diagram of a full bridge inverter using ic cd4047? I would like to construct a 5000w inverter,thank you.

Hi Evans, you can try the first circuit from this article:

https://www.homemade-circuits.com/5kva-transformerless-inverter-circuit/

Hello sir,the circuit above uses 4049,but I would like one that uses CD4047 and a transformer without centre tap and n channel mosfets

Evans, please check the first circuit in the link which I gave you in the previous comment…

Hello good morning my name is Carlos from Argentina. I have a question, on the web I found this wave inverter circuit modifies https://www.homemade-circuits.com/wp-content/uploads/2019/08/modified-full-bridge.png I want to know if it can really work? From already thank you very much.

Hi Carlos,

It will need to be tested practically, because as you can see the two ICs are cascaded with each other which is difficult to simulate in mind. So it will need to be tested for verifying the results.

Hello, good afternoon, my name is Carlos from Argentina, I am a faithful follower of the website. I want to build the inverter with lm555 and cd4017 with bridge H and 4 mosfet .. The question is I have a transformer of 12v x 15 amps without central cover how much power I will have output .. Thank you very much.

Atte: Carlos from Argentina

Thank you Carlos, you will be able to get a maximum of 12 x 15 = 180 watts, or may be around 160 watts

Many thanks for the complements, I appreciate it. Please keep up the good work!

Ok no problem, I don’t trust the Chinese or there electronics. I sent you another message about that. Hay if all else fails with this module. I know where to get circuits that have been tested. Thanks for everything you have done. As they say in the U.S. you are a good man Charley Brown.

I have not yet used the mentioned product so I am not sure about its performance.

Good deal thanks, I have been playing around with a few of your circuits have not decided which one it will be a pure sign wave one, I was wondering what you thought of the Chinese version SPWM egs002

Thank you for trusting my suggestions.

If you connect the AC output voltage to the mosfets first, while the oscillator is switched OFF then nothing will happen, since all the mosfets will remain switched OFF. However, in this situation if you switch ON the oscillator then initially for a fraction of a second the mosfets could be switched ON randomly causing short circuits or some unexpected results.

Therefore it is always a good practice to switch ON the oscillator fist and then switch ON the voltage to the mosfets

Quick question about the h-bridge, since I am using two voltage one for the oscillator and another voltage for the ac output, I read that I need to turn on the oscillator first then apply the high voltage DC second. Is this correct ? You are a wise man your word is gold. Everything I have built from you has worked, still working on the solar inverter, I have come a long way almost there.

I have updated the design under this article:

https://www.homemade-circuits.com/2014/01/simplest-full-bridge-inverter-circuit.html